# For Distributed Generation Systems Grid Voltage Synchronization under Various Grid Fault Conditions

### Jagadeesh. Peddapudi, Balachandrareddy.C

EEE DEPT, SSUTMS, Sehore, MP, India

#### **ABSTRACT**

The actual grid code requirements for the grid connection of distributed generation systems, it is mainly wind and photovoltaic (PV) systems are becoming very demanding. The transmission system operators (TSOs) are especially concerned about the low-voltage-ride-through requirements. Solutions based on the installation of STATCOMs and dynamic voltage regulators (DVRs), as well as on advanced control functionalities for the existing power converters of distributed generation plants, have contributed to enhance their response under faulty and also distorted scenarios and, hence, to fulfil these requirements effectively. In order to achieve satisfactory results with such systems, it is necessary to count on accurate and fast grid voltage synchronization algorithms, which are able to do work under unbalanced and distorted conditions. This paper analyzes the synchronization capability of three advanced synchronization systems: the decoupled double synchronous reference frame phase-locked loop (PLL), the dual second order generalized integrator PLL, and the three-phase enhanced PLL, designed to work under such conditions. Although other systems based on frequency-locked loops have also been developed, PLLs have been chosen due to their link with dq0 controllers. In the following, the different algorithms will be presented and discretized, and their performance will be tested in an experimental setup controlled in order to evaluate their accuracy and implementation features

Keywords: Electric variable measurements, electrical engineering, frequency estimation, frequency-locked loops, harmonic analysis, monitoring, synchronization

#### **I.INTRODUCTION**

The power share of renewable energy-based generation sys-tems is supposed to reach 20% by 2030, where wind and photovoltaic (PV) systems are assumed to be the most outstand-ing examples of integration of such systems in the electrical Manuscript received September 2, 2013; revised February 4, 2014 and April 12, 2014; accepted May 15, 2014. Date of publication January 13, 2015; date of current version July 15, 2015. Paper 2012-SECSC-582.R2, presented at the 2012 IEEE Energy Conversion Congress and Exposition, Raleigh, NC, USA, September 15–20, and approved for publication in the IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS by the Sustainable Energy Conversion Systems Committee of the IEEE Industry Applications Society. This work was sup-ported by the Spanish Ministry of Economy and Competitiveness under Project ENE2013-48428-C2-2-R.

A. Luna, J. Rocabert, J. I. Candela, and J. R. Hermoso are with the Department of Electrical Engineering, Technical University of Catalonia. Teodorescu and F. Blaabjerg are with the Department of Energy Systems,

# Volume No.06, Special Issue No.(01), December 2017 IJARSE WWW.ijarse.com ISSN: 2319-8354

Aalborg University, 9220 Aalborg East, Denmark. P. Rodriguez is with the Department of Electrical Engineering, Technical University of Catalonia, 08222 Barcelona, Spain, and also with Abengoa, 41014 Seville, Spain Colour versions of one or more of the figures in this paper are. Digital Object Identifier 10.1109/TIA.2015.2391436 network [1].

The increased penetration of these technologies in the electrical network has reinforced the already existing concern among the transmission system operators (TSOs) about their influence in the grid stability; as a consequence, the grid connection standards are becoming more and more restrictive for distribution generation systems in all countries [2]–[6]. In the actual grid code requirements (GCRs), special constraints for the operation of such plants under grid voltage fault conditions have gained a great importance. These requirements determine the fault boundaries among those through which a grid-connected generation system shall remain connected to the network, giving rise to specific voltage profiles that specify the depth and clearance time of the voltage sags that they must withstand. Such requirements are known as low voltage ride through (LVRT) and are described by a voltage versus time characteristic [7].

Although the LVRT requirements in the different standards are very different, as shown in [8], the first issue that generation systems must afford when a voltage sag occurs is the limitation of their transient response, in order to avoid its protective disconnection from the network. This is the case, for instance, of fixed speed wind turbines based on squirrel cage induction generators, where the voltage drop in the stator windings can conduct the generator to an over speed tripping, as shown in [9]. Likewise, variable speed wind power systems may lose controllability in the injection of active/reactive power due to the disconnection of the rotor side converter under such conditions [10], [11]. Likewise, PV systems would also be affected by the same lack of current controllability.

Solutions based on the development of auxiliary systems, such as STATCOMs and dynamic voltage regulators (DVRs), have played a decisive role in enhancing the fault ride through (FRT) capability of distributed generation systems, as demonstrated in [12]–[16]. Likewise, advanced control functionalities for the power converters have also been proposed [17], [18]. In any case, a fast detection of the fault contributes to improving the effects of these solutions; therefore, the synchronization algorithms are crucial.

In certain countries, the TSOs also provide the active/reactive power pattern to be injected into the network during a voltage sag; this is the case for the German E-on [2] and the Spanish Red Eléctrical Española (REE) [3]. This trend has been followed by the rest of the TSOs; moreover, it is believed that this operation requirement will be extended, and specific demands for balanced and unbalanced sags will arise in the following versions of the grid codes worldwide [19].

Regarding the operation of the distributed generation systems under balanced and unbalanced fault conditions, relevant contributions, such as [20]–[29], can be found in the literature. These solutions are based on advanced control systems that need to have accurate information of the grid voltage variables in order to work properly, something that has prompted the importance of grid synchronization algorithms. In power systems, the synchronous reference frame PLL (SRF PLL) is the most extended technique for synchronizing with three-phase systems

[30]. Nevertheless, despite the fact that the performance of SRF PLL is satisfactory under balanced conditions, its response can be inadequate under unbalanced, faulty, or distorted conditions [31]–[33].

In this paper, three improved and advanced grid synchronization systems are studied and evaluated: the decoupled double synchronous reference frame PLL (DDSRF PLL) [34], the dual second order generalized integrator PLL (DSOGI PLL), [35] and the three-phase enhanced PLL (3phEPLL) [36]. Their performance, computational cost, and reliability of the amplitude and phase detection of the positive sequence of the voltage, under unbalanced and distorted situations, have been evaluated according to experimental grid fault patterns extracted fromand [38], which have been reproduced in a real scaled electrical network.

In the following sections, the discrete representation of each PLL will be detailed (see Section IV), due to its great importance in the final implementation of the control, after a brief description of the different structures (see Section III). Finally, their behaviour will be tested in an experimental setup (see Section VI), and their performance will be discussed, particularly taking into account the accuracy of the positive-sequence detection and their computational cost (see Section VII) when considering different faulty scenarios, covering the response in front of sags, frequency changes, and harmonic immunity.

#### II. GRID SYNCHRONIZATION SPECIFICATIONS BASED ON GCR

Even though several works are published within the field of grid synchronization, almost all of them are centered on analyzing the individual dynamic performance of each proposal, without first determining a time response window within the dynamic behaviour of the system under test, which would be considered to be satisfactory. In this paper, in order to evaluate the response of the grid synchronization topologies under test, a common performance requirement for all the structures has been established in this section, considering the needs that can be derived from the LVRT requirements. Despite the fact that the detection of the fault can be carried out with simpler algorithms, as shown in [39] and [40], the importance of advanced grid synchronization systems lies in the necessity of having accurate information about the magnitude and phase of the grid voltage during the fault, in order to inject the reactive power required by the TSO. In the German standard [2], it is stated that voltage control must take place within 20 ms after the fault recognition, by providing a reactive current on the low voltage side of the

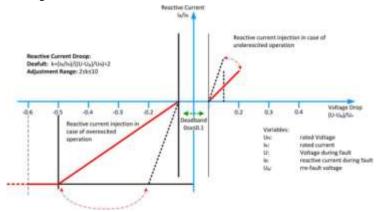

Fig. 1. E-on voltage support requirement in the event of grid fault.

Fig. 2. REE voltage support requirement in the event of grid fault.

Generator transformers to at least 2% of the rated current for each percent of the voltage dip, as shown in Fig. 1. 100% reactive power delivery must be possible, if necessary. A similar condition is given in the Spanish grid code, where the wind power plants are required to stop drawing inductive reactive power within 100 ms of a voltage drop and be able to inject full reactive power after 150 ms, as shown in Fig. 2. Considering these demands, this paper will consider that the estimation of the voltage conditions will be carried out within 20–25 ms, as this target permits it to fulfil the most restrictive requirements, in terms of dynamical response, available in the grid codes. This condition will be extended to frequency estimation; although this parameter is more related to secondary control algorithms than LVRT, the same time window between 20 and 25 ms will be considered in this work for the detection of the disturbance.

### III. DESCRIPTION OF THE THREE SYNCHRONIZATION SYSTEMS

Many of the positive-sequence detection algorithms are based on SRF PLLs [32]. Despite having a good response under balanced conditions, their performance becomes insufficient in unbalanced faulty grids (95% of cases), and their good opera-tion is highly conditioned to the frequency stability, which is incompatible with the idea of a robust synchronization system. Many authors have discussed different advanced models, which

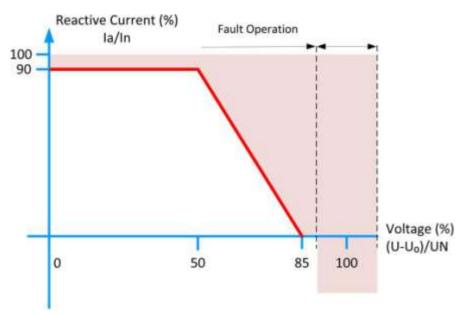

Fig. 3. DDSRF-PLL block diagram.

Fig. 4. DSOGI-PLL block diagram

are able to overcome the problems of the classical PLL, using frequency and amplitude adaptive structures which are able to deal with unbalanced, faulty, and harmonic-polluted grids. In the framework of these topologies, three PLL structures will be discussed and evaluated in this paper.

#### A. DDSRF PLL

The DDSRF PLL, published in [34] and [41], was developed for improving the conventional SRF PLL. This synchronization system exploits two synchronous reference frames rotating at the fundamental utility frequency, one counter clockwise and another one clockwise, in order to achieve an accurate detection of the positive- and negative-sequence components of the grid voltage vector when it is affected by unbalanced grid faults. The diagram of the DDSRF PLL is shown in Fig. 3.

When the three-phase grid voltage is unbalanced, the funda-mental positive-sequence voltage vector appears as a dc voltage on the  $dq^{+1}$  axes of the positive-sequence SRF and as ac voltages at twice the fundamental utility frequency on the  $dq^{-1}$  axes of the negative-sequence SRF. In contrast, the negative-sequence voltage vector will cause a dc component on the negative-sequence SRF and an ac oscillation on the positive-sequence SRF. Since the amplitude of the oscillation on the positive-sequence SRF matches the dc level on the negative-sequence SRF and vice versa, a decoupling network is applied to signals on the dq positive/negative SRF axes in order to cancel out such ac oscillations. Low-pass filters (LPFs) in Fig. 3 are responsible for extracting the dc component from the signal on the decoupled SRF axes. These dc components collect information about the amplitude and phase angle of the positive- and negative-sequence components of the grid voltage vector.

Finally, the PI controller of the DDSRF PLL works on the decoupled q-axis signal of the positive sequence SRF  $(v_q^*_{+1})$  and performs the same function as in an SRF PLL, aligning the positive-sequence voltage with the d-axis. This signal is free of ac components due to the effect of the decoupling networks; the bandwidth of the loop controller can be consequently increased.

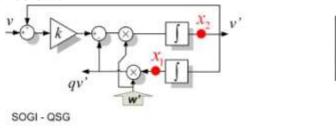

### B. DSOGI PLL

The operating principle of the DSOGI PLL for estimating the positive- and negative-sequence components of the grid voltage vectors is based on using the instantaneous symmetrical component (ISC) method on the  $\alpha$   $\beta$  stationary reference frame, as explained in [35]. The diagram of the DSOGI PLL is shown in Fig. 4. As it can be noticed, the ISC method is implemented by the positive-sequence calculation block.

To apply the ISC method, it is necessary to have a set of signals,  $v_{\alpha}$ – $v_{\beta}$ , representing the input voltage vector on the  $\alpha\beta$  stationary reference frame together with another set of signals,  $qv_{\alpha}$ – $qv_{\beta}$ , which are in quadrature and lagged with respect to  $v_{\alpha}$ – $v_{\beta}$ . In the DSOGI PLL, the signals to be supplied to the ISC method are obtained by using a dual second order generalized integrator (DSOGI), which is an adaptive band-pass filter based on the generalized integrator concept [42]. At its output, the DSOGI provides four signals, namely,  $v_{\alpha}$  and  $v_{\beta}$ , which are filtered versions of  $v_{\alpha}$  and  $v_{\beta}$ , respectively, and  $qv_{\alpha}$  and  $qv_{\beta}$ , which are the in quadrature versions of  $v_{\alpha}$  and  $v_{\beta}$ . A conventional SRF PLL is applied on the estimated positive-sequence voltage vector,  $v_{\alpha\beta}^+$ , to make this synchro-nization system frequency adaptive. In particular, the  $v_{\alpha\beta}^+$  volt-age vector is translated to the rotating SRF, and the signal on the q-axis,  $v_q^+$ , is applied at the input of the loop controller. As a consequence, the fundamental grid frequency ( $\omega$ ) and the phase angle of the positive-sequence voltage vector ( $\theta^+$ ) are estimated by this loop. The estimated frequency for the fundamental grid component is fed back to adapt the center frequency  $\omega$  of the DSOGI.

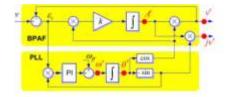

#### C. 3phEPLL

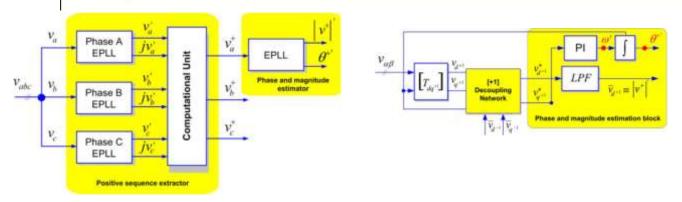

The enhanced phase-locked loop (EPLL) is a synchronization system that has proven to provide good results in single-phase synchronization systems [43]. An EPLL is essentially an adaptive band pass filter, which is able to adjust the cut-off frequency as a function of the input signal. Its structure was later adapted for the three-phase case [44], in order to detect the positive-sequence vector of three-phase signals, obtaining the 3phEPLL that is represented in Fig. 5.

In this case, each phase voltage is processed independently by an EPLL. This block filters the input signal and generates two sinusoidal outputs of the same amplitude and frequency,  $v_n$  and  $jv_n$ , the second one being 90° with respect to  $v_n$ . The resulting signals constitute the input for the computational unit. Owing to these in-quadrature signals, the instantaneous positive-sequence voltage component,  $v_{abc}^+$ , can be estimated by means of using the ISC method.

### IV. DISCRETE IMPLEMENTATION

The performance of the different structures under test is really dependent on their final digital implementation, particularly on

Fig. 5. 3phEPLL block diagram Fig. 6.Phase and magnitude estimation loop of the DDSRF PLL.

the discretization approach made to their continuous equations. This implementation is critical and should be studied in detail as a straightforward implementation can give rise to additional delays in the loop that hinder the good performance of the PLL. Some methods, such as the forward Euler, the backward Euler, and the Tustin (trapezoidal) numerical integration, offer a good performance when used for discretizing other synchronization systems, as shown in [46] and [47]. However, Euler methods can be inadequate under certain conditions, due to the need of introducing additional sample delays [48]. Therefore, according to the specific needs of the presented topologies, this section will describe the discrete representation of each PLL individually. In order to facilitate the comprehension of the process, the different building blocks that appear at Figs. 3–5 will be referenced. The values of the different parameters used in each case are summarized in the Appendix.

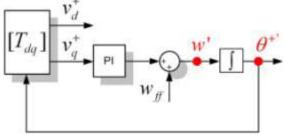

#### A. DDSRF-PLL Discretization

The discrete model of this PLL can be easily obtained since the continuous representation of several parts does not change in the discrete domain. This is the case for the transformation blocks  $T_{\alpha\beta}$ ,  $T_{dq}+1$ , and  $T_{dq}-1$ , whose description can be found in general scope literature [49].

1) Positive- and Negative-Sequence Decoupling Networks: The decoupling network constitutes one of the most important contributions of this synchronization method. The discrete equations of these blocks are shown in (1), being almost the

same as in the continuous domain [41]. It is just necessary to consider one sample delay of  $\theta$ ,  $v^-_d-1$ ,  $v^-_q-1$ ,  $v^-_d+1$ , and  $v^-_q+1$  in order to avoid algebraic loops. *Phase and Magnitude Estimator Discretization:* In the DDSRF PLL, the decoupling network appears embedded in the classical SRF-PLL loop (see Fig. 6). However,

this does not affect the discretization of the phase and magnitude estimator since  $v_{q+1}^*$  and  $v_{q+1}^*$  act as the input

of this block

$$v_{d_{+1}}^{*}[n+1]$$

$$\begin{aligned} v_{q+1}^{*} & [n+1] \\ & V_{q+1} & [n+1] \\ & & & & \\ 1 & 0 & V_{d+1} & [n+1] \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & &$$

The discrete controller and the integrator can be built using a backward numerical approximation. The frequency and phase can then be represented in the z-domain (2), considering  $v_{q+1}^*$  as the error to be minimized. In this equation, a feed forward of the nominal frequency is given by means of  $\omega_{ff}$

$$W(z) = \begin{pmatrix} (k_p + k_i & T_s)z & k_p & V^* \\ & \ddots & & & \\ & & - & & \\ \hline \theta^+ = & \frac{T_{s \cdot Z}}{z} \cdot W(z). \end{pmatrix} \qquad (2)$$

Finally, sample-based representation gives rise to (3), which are the expressions to be implemented

$$\omega \quad [n+1] = \omega [n] - k_p \cdot v_{q+1}^* [n] + (k_p + k_i \cdot T_s) \cdot v_{q+1}^* [n+1]$$

$$\theta^{+}[n+1] = \theta^{+}[n] + T_{S} \cdot \omega[n+1].$$

(3)

In these equations, a frequency feed forward has been introduced as an initial condition to  $\omega$ .

3) LPF Block Discretization: The amplitudes of the dq positive- and negative-sequence components are the outputs of the decoupling networks. However, four infinite impulse response (IIR) LPFs extract the ripple from each sequence estimation in order to reinforce the performance of the PLL

in case of harmonic pollution. A first-order filter with a cut-off frequency  $\omega_f$ , equal to half of the grid frequency, was originally proposed in [41]; hence, the same transfer function has been implemented in this paper for evaluation purposes in

$$y[n] = \frac{1}{T_{S} \cdot \omega_{f} + 1} \cdot x[n] + \frac{T_{S} \cdot \omega_{f}}{T_{S} \cdot \omega_{f} + 1} \cdot u[n]$$

$$x[n+1] = y[n]. \tag{4}$$

#### B. DSOGI-PLL Discretization

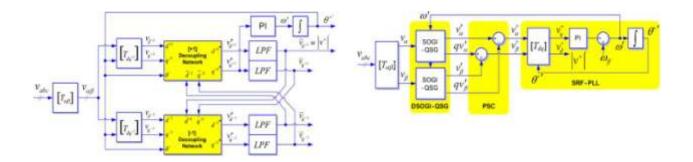

1) DSOGI-QSG Block Discretization: As was previously mentioned in Section II, the DSOGI-based quadrature signal generator (QSG) of Fig. 4 consists of two independent and decoupled second-order generalized integrators (SOGIs). Therefore, each SOGI-based quadrature signal generator can be discretized individually, thus facilitating its mathematical description. In Fig. 7, the block diagram of the implemented SOGI is shown.

Fig. 7. Quadrature signal generator based on a second order generalized integrator (SOGI QSG).

Fig. 8. State variables of the SRFPLL block.

This quadrature signal generator (QSG) is a linear system itself; therefore, a discrete representation can be systematically obtained if the continuous state space is previously deducted. The equations of the SOGI state space appear detailed in (5). where v constitutes the input while v and qv are the two in-quadrature output signals

$$x'_n = A x_n + B \cdot v$$

$x_1 \quad y_n = v$

## International Journal of Advance Research in Science and Engineering

## Volume No.06, Special Issue No.(01), December 2017

### www.ijarse.com

$$y_n = C^{-}x_n$$

;  $x_n = {}_{x2}$   $qv$  .

$A = {}_{-\omega} 2$   $-k \cdot \omega$   $B = {}_{k \cdot \omega}$   $C = {}_{\omega}$  0 . (5)

0 1 0 0 1

The discretization of this system has been performed using trapezoidal integrators, as they offer a better detection of the phase, which is important when dealing with sinusoidal signals

- [22]. The symbolic values of each matrix of (7) are detailed in

- (6), shown at the bottom of the page. In these matrices,  $T_s$  is the sampling time of the discrete system,  $\omega$  [n] is the estimated frequency magnitude, which comes from the estimation made at the SRF-PLL block at each computation step, and k is the SOGI gain [14]

$$x[n+1] = A \cdot x[n] + B \cdot v[n]$$

$$y[n] = C \cdot x[n] + D \cdot v[n]. \tag{7}$$

The discrete state space of (6) is obtained from the continuous representation by means of the mathematical procedure presented in (8) [50], [51]

where  $T_s$  is the sampling time.

The resulting discrete system is the best option as it reduces the need of using additional delays for breaking algebraic loops that appear using other methods which do not consider the SOGI QSG as a whole.

2) SRF PLL Discretization: The frequency and phase detection is obtained by means of the SRF PLL shown in Fig. 8. The discretization of the controller and the integrator is performed using the backward numerical approximation.

The frequency and phase can then be represented in the z-domain, as shown in (9), where  $v_q^+$  constitutes the error to be minimized

$$W(z) = \begin{cases} (k_p + k_i & T_s)z & k_p \\ z & \cdot 1 & - & \cdot V^* & (z) + \omega ff \\ & & +1 \end{cases}$$

$$- \frac{T}{s \cdot z}$$

$$\theta^+ = \frac{z \cdot 1}{z} \cdot W(z). \tag{9}$$

### www.ijarse.com

It can be noticed that the previous equations in (9) are equal to (2), as, in both cases, an SRF PLL is implemented. Like-wise, the sample-based representation of (9) can be written as shown in

$$w[n+1] = \omega[n] - k_p \cdot v_{q+1}^*[n] + (k_p + k_i \cdot T_s) \cdot v_{q+1}^*[n+1]$$

$$\theta^{+}[n+1] = \theta^{+}[n] + T_{s} \cdot \omega[n+1].$$

(10)

### C. 3phEPLL Discretization

This three-phase grid synchronization system exploits the EPLL as a quadrature signal generator. An independent EPLL is used for processing each one of the three-phase voltages. The same EPLL structure is applied again to detect the magnitude and phase of the positive-sequence voltage component.

1) QSG Block—EPLL Discretization: The block diagram of the EPLL implemented in this paper is presented in Fig. 9

$$4 + 2T_{s} \cdot k \cdot \omega [n] - T^{2} \cdot \omega [n]^{2}$$

$$A = \gamma_{-4Ts \cdot \omega [n]} 2^{s}$$

$$C = \gamma \qquad -2T_{s}^{2} \cdot \omega [n]^{2}$$

$$2T_{s} \cdot \omega [n] \cdot (2 + T_{s} \cdot k \cdot \omega [n])$$

$$1$$

$$\gamma =$$

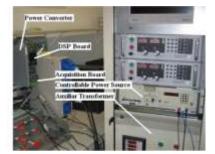

Fig. 9.Quadrature signal generator based on an EPLL structure. Fig. 10. Experimental setup for testing three different synchronization algorithms

# International Journal of Advance Research in Science and Engineering 🔑

## Volume No.06, Special Issue No.(01), December 2017

### www.ijarse.com

IJARSE ISSN: 2319-8354

According to this diagram, the state space representation of the EPLL in the continuous domain can be written as shown in

$$A'(t) = k \quad e(t) \quad \cos \theta \ (t)$$

$$...$$

$$\omega'(t) = -k_i \cdot e(t) \cdot \sin \theta \ (t)$$

$$k_p$$

$$...$$

$$\theta'(t) = \omega \ (t) + \overline{k_i} \ \omega' \ (t). \tag{11}$$

The discrete state space variable representation was de-scribed in [44] using a forward Euler approximation to reach satisfactory results; therefore, the same method has been im-plemented here

$$e[n+1] = u[n+1]-v[n]$$

$$A[n+1] = A[n] + T_s \cdot k \cdot e[n] \cdot \cos(\theta[n])$$

$$\omega \qquad [n+1] = \omega [n] - T_s \cdot k_i \cdot e[n] \cdot \sin (\theta [n])$$

$$\theta \qquad [n+1] = \theta [n] + T_s \cdot \omega [n] - T_s \cdot k_p \cdot e[n] \cdot \sin (\theta [n]). \tag{12}$$

Finally, after the state variables are calculated, the EPLL output can be obtained by (13), generating the two quadrature signals

$$v[n+1] = A[n+1] \cdot \cos(\theta[n+1])$$

$$qv[n+1] = -A[n+1] \cdot \sin(\theta[n+1]).$$

(13)

PROPERTIES OF THE TESTING VOLTAGE SAGS

TABLE I

A Sag B Sag C Sag D Sag

$$\begin{bmatrix} V^+ = 40 | -40^o \\ V^- = 0 | \underline{0}^o \end{bmatrix} \begin{bmatrix} V^+ = 73.3 | -10^o \\ V^- = 26.6 | \underline{170^o} \\ V^0 = 0 | \underline{0}^o \end{bmatrix} \begin{bmatrix} V^+ = 67.37 | -5.7^o \\ V^- = 27.81 | \underline{12.2^o} \\ V^+ = 0 | \underline{0}^o \end{bmatrix} \begin{bmatrix} V^+ = 67.37 | -5.7^o \\ V^- = 27.81 | \underline{12.2^o} \\ V^+ = 0 | \underline{0}^o \end{bmatrix} \begin{bmatrix} V^+ = 67.37 | -5.7^o \\ V^- = 27.81 | \underline{177.8^o} \\ V^+ = 0 | \underline{0}^o \end{bmatrix}$$

Positive, negative and homopolar sequence vectors during the fault conditions for the different sags

# Volume No.06, Special Issue No.(01), December 2017

### www.ijarse.com

However, for the phase and magnitude detection block, the outputs are the positive sequence magnitude and phase, which correspond directly with the states  $\theta$  and A, respectively

This type of discretization method needs a more accurate tuning, due to the fact that the stable regions of the splane and z-plane are different, However, its major simplicity, compared to the Tustin or backward integration, benefits from the computational speed of this block.

- 2) computational Block Unit: The description for this block is the same in both discrete and continuous domains. Nevertheless, specific equations are used in this paper, as shown.

- 3) *Phase and Magnitude Detection Block:* This element is based on another EPLL, which is responsible for estimating the phase and the magnitude of the positive-sequence fundamental component. Its discretization is equal to that shown in(12)

$$v^{+}[n] = \frac{1}{3}v[n] - \frac{1}{6}(v[n] + v[n]) + \frac{1}{2\sqrt{3}}(jv[n]) + \frac{1}{2}v[n]$$

$$v^{+}[n] = \frac{1}{2}v[n] - \frac{1}{2}(v[n] - v[n]) + \frac{1}{2^{\frac{1}{3}}}(jv[n] - jv - [n])$$

$$c - 3 - c - 6a - b - 2^{\frac{1}{3}}a - b$$

$$v_{b}^{+}[n] = -v_{a}^{+}[n] + v_{c}^{+}[n] .$$

### V. TESTING SIGNALS AND EXPERIMENTAL SETUP

Following the representations in the discrete domain already deducted, the different PLL algorithms have been implemented in a control board based on a floating-point Texas Instruments TMS320F28335 DSP at 150 MHz (6.67-ns cycle time). Their capability to perform a fast and accurate synchronization has been tested in the laboratory under different grid fault scenarios where the three-phase voltage waveforms experience transients due to the appearance of voltage sags, frequency variations, and harmonic pollution. These unbalanced and distorted input volt ages were generated by means of an ac programmable source and an auxiliary transformer. The layout of the experimental workbench used in this paper is presented in Fig. 10. Six representative faulty and distorted scenarios have been selected for evaluating the three synchronization systems under test *Voltage sags*: In Table I, the characteristics of four selected

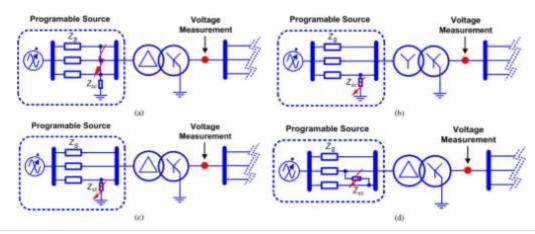

Fig. 11. Generation of grid voltage sags in the experimental setup.

www.ijarse.com

- (a) Generation of a Type "A" voltage sag. (b) Generation of a Type "B" voltage sag.

- (c) Generation of a Type "C" voltage sag. (d) Generation of a Type "D" voltage sag

that these sags are the most characteristic ones that affect wind power systems. In Table I, the magnitude and the phase of the symmetrical components of the voltage dur-ing the fault period are indicated in each case, assuming that the prefault voltage is always equal to  $V^+ = 100$ ,  $V^- = 0$ , and  $V^0 = 0$ .

As can be seen in the table, three of the proposed sags give rise to unbalanced voltages, as explained in [37] and [38], and, hence, to positive- and negative-sequence components. The presence of the negative sequence during the fault allows a more rigorous analysis of the synchronization capability of the different algorithms under test. Moreover, unbalanced faults constitute 95% of the voltage sags that affect distributed generation systems. In order to obtain the aforementioned dips, different faults have been emulated with the programmable ac source at the primary winding of the transformer, as indicated in Fig. 11. De-pending on the fault topology as well as on the connection of the transformer, the desired voltage waveforms at the measurement point, indicated in Table I, are finally obtained, acquired, and later processed by the DSP.

- *Harmonic-polluted voltage* (8% *THD*): According to the EN50160 standard [53], the THD of the voltage wave-forms at the output of a generation facility cannot be higher than 8%. Considering this requirement, Table II shows the harmonic composition used for evaluating the performance of the grid synchronization systems under test when the grid voltages become distorted.

- *Grid voltage frequency jumps*: By means of the pro-grammable source, a 10-Hz jump (from 50 to 60 Hz) in the frequency value of the positive sequence has been applied to analyze the response of the frequency adaptive structures under test.

In the following section, the responses of the DDSRF PLL, DSOGI PLL, and 3PhEPLL under these transient conditions will be compared.

TABLE II

HARMONIC COMPOSITION FOR THE TEST

| Order of the harmonic | THD (%) |

|-----------------------|---------|

| 2 <sup>nd</sup>       | 2%      |

| 4th                   | 1%      |

| 5 <sup>th</sup>       | 5%      |

| 700                   | 4%      |

| 11th                  | 3%      |

| 13 <sup>th</sup>      | 3%      |

Values of individual harmonic voltages at the supply terminals for orders up to 25, given in percent of the nominal supply voltage in RMS

### VI. EXPERIMENTAL PERFORMANCE OF THE PLLS UNDER TEST

A. Behaviour in Case of Voltage Sags

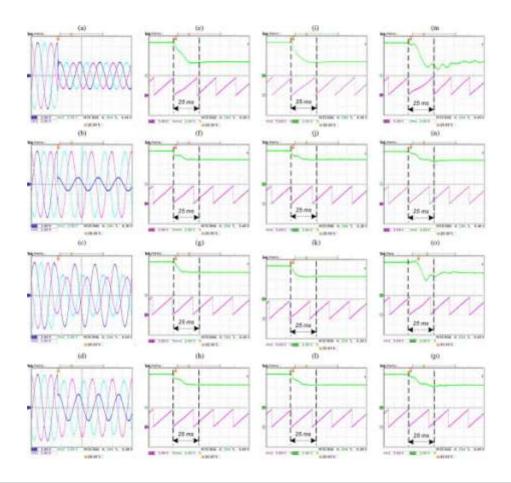

Type "A" Sag Test: This kind of voltage sag appears as a consequence of three-phase faults that give rise to high short circuit currents and, hence, to a balanced voltage drop in the network. As Fig. 12(e) and (i) shows, the DDSRF PLL and the DSOGI PLL produce a good response, as both systems achieve a very fast detection (20 ms) of the positive-sequence components (less than two cycles). The response of the 3phEPLL

- 1) depicted in Fig. 12(m), also shows a good response, but with a larger transient in the positive-sequence estimation.

- 2) Type "B" Sag Test: This kind of fault permits analyzing the behavior of the PLLs under test in the presence of zero-sequence components at the input. The Clarke transformation used in DSOGI PLL and DDSRF PLL to extract the  $\alpha\beta$  components enhances the response of this synchronization system when the faulty grid voltage presents zero-sequence components. Their responses, as shown in Fig. 12(f) and (j), are fast and accurate. On the other hand, the 3phEPLL does not cancel out the zero-sequence component from the input voltage, some-thing which may affect the dynamics of the positive-sequence estimation loop. However, this effect is further attenuated by the computational unit, as Fig. 12(n) shows; the steady-state response is also reached with no great delay, as detailed in

Fig. 12(n), showing the good behaviour of this PLL under these conditions.

3) Type "C" and "D" Sag Tests: These kinds of sags appear due to phase-to-ground and phase-to-phase short circuits at the primary winding of the transformer, respectively, as shown in Table I. In a distribution network, these distortions are more common than the previous ones, as they are the typical grid faults caused by lightning storms. As depicted in Fig. 12(g)–(p), all three PLLs permit detecting the positive sequence between 20 and 30 ms; however, the 3phEPLL has a slower stabilization, as shown in Fig. 12(o) and (p). This effect is a bit more noticeable with the "C" sag, where the combination of the phase

jump and the magnitude change of two phases occurs, as shown in Fig. 12(o).

### B. Frequency Changes (50–60 Hz)

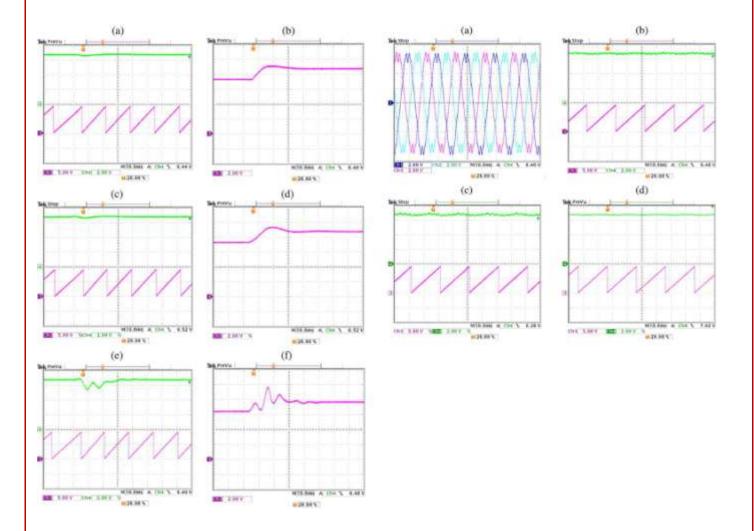

In this experiment, similar results are obtained with the DDSRF and the DSOGI PLL, as can be seen in Fig. 13(a)–(d). The low overshooting in the amplitude estimation in both cases [see Fig. 13(a) and (c)] assists the

good phase and frequency detection, as shown in Fig. 13(b) and (d). Likewise, the response of the 3phEPLL shows a similar settling time, as shown in Fig. 13(e); however, the initial oscillation in the

### NUMBER OF OPERATIONS PERFORMED BY EACH PLL

| Structure   | A  | M  | T   | S.  | D |

|-------------|----|----|-----|-----|---|

| DDSRF-PLL   | 22 | 32 | 1.2 | 14  | 0 |

| DSOGI-PLL   | 38 | 86 | 4   | 8   | 2 |

| 3phEPLL-PLL | 42 | 41 | 19  | 16. | 0 |

A = Addition M = Multiplication T = Trigonometric S = Variable storage D = Division. Type and number of operations in each PLL. The shadowed cells indicate the synchronization system that is used the least number of times by each operator.

amplitude estimation of the voltage contributes to slightly de-lay the stabilization of the frequency magnitude, as displayed in Fig. 13(f).

C. Polluted Grids (THD = 8%)

The 3phEPLL behaves as a band pass filter for the input signal, something that permits filtering the input without adding extra filters. As can be seen in Fig. 14(d), the 3phEPLL offers the best filtering capability among the PLLs under test, with a clear and undistorted estimation of the magnitude and phase of the input.

The response of the DDSRF PLL, depicted in Fig. 14(b), which has a first-order filter at the output, is even better than the one provided by the DSOGI PLL, due to the latter's low-pass filtering behavior. Although the DSOGI PLL also behaves as well as a bandpass filter, the tuning of its parameters, which permits a faster stabilization of the estimated signal in the previous tests, plays against its immunity in front of harmonics, as shown in Fig. 14(c), giving rise to small oscillations in the positive-sequence estimation.

### VII. EVALUATION OF THE COMPUTATIONAL BURDEN TIME

| Structure   | Execution Time |  |  |

|-------------|----------------|--|--|

| DDSRF-PLL   | 5.41 µs        |  |  |

| DSOGI-PLL   | 5.91 µs        |  |  |

| 3phEPLL-PLL | 8.36µs         |  |  |

Global burden time of one cycle of instructions for each PLL programmed in a TMS320F28335 DSP.

| DDSRF-FLL                 | Values            |

|---------------------------|-------------------|

| T,                        | 100 µs            |

| $k_{\mu}$                 | 2.22              |

| $k_z$                     | 246.74            |

| $\omega_{\mathcal{J}}$    | 314.1592 rad/s    |

| 07                        | 157.0796 rad/s    |

| DSOGI-PLL                 | Values            |

| T,                        | $100 \mu s$       |

| $k_{_{T}}$                | 2.22              |

| $k_i$                     | 61.7              |

| k                         | $\sqrt{2}$        |

| $\omega_{\mathcal{J}}$    | 314.1592 rad/s    |

| 3phEPLL-PLL               | Values            |

| opiner current            | v annes           |

| T,                        | 100 µs            |

| T,                        |                   |

| _                         | $100 \mu s$       |

| $T_r$ $k_p$               | 100μs<br>5        |

| $T_{\nu}$ $k_{p}$ $k_{i}$ | 100µs<br>5<br>450 |

DISCREDIT

# Volume No.06, Special Issue No.(01), December 2017 IJARSE WWW.ijarse.com ISSN: 2319-8354

and multiplications to be calculated, the DSOGI PLL holds second position in this burden-time comparative, although the differences with respect to the DDSRF are not quite significant. Finally, it can be observed that the greatest burden time is obtained with the 3phEPLL.

#### VIII. CONCLUSION

This paper studied the behavior of three advanced grid synchronization systems. Their structures have been presented, and their discrete algorithms have been detailed. Moreover, their performances have been tested in an experimental setup, where these algorithms have been digitally implemented in a commercial DSP, allowing proof of their satisfactory response under balanced and distorted grid conditions.

The DDSRF PLL and the DSOGI PLL allow estimating the ISCs of a three-phase system working in the  $\alpha\beta$  reference frame, while the 3phEPLL uses the "abc" reference frame, thus working with three variables. As has been shown, this feature simplifies the structure of the DSOGI PLL and the DDSRF PLL, which allows reducing the computational burden, as com-pared to the 3phEPLL, without affecting its performance.

The synchronization capability of the three PLLs under test has been shown to be fast and accurate under faulty scenarios, allowing the detection of the positive sequence of the voltage in 20–25 ms in all cases; however, the simpler structure of the DDSRF and the DSOGI affords an easier tuning of their control parameters and, therefore, a more accurate control of their transient response.

The immunity of the analyzed PLLs in the possibility of a polluted network is better when using the 3phEPLL and the DDSRF, due to their greater bandpass and low-pass filtering capabilities. Although the DSOGI also gives rise to reasonably good results, due to its inherent bandpass filtering structure, its response is more affected by harmonics.

Although all three have been shown to be appropriate for synchronizing with the network voltage in distributed power generation applications, mainly PV and wind power, the lower computational cost of the DDSRF PLL and the DSOGI PLL, together with their robust estimation of the voltage parameters, offers a better tradeoff between the presented systems, making them particularly suitable for wind power applications.

#### **APPENDIX**

The parameters used for tuning the different advanced syn-chronization systems analyzed in this paper are summarized in Table V.

# Volume No.06, Special Issue No.(01), December 2017 IJARSE WWW.ijarse.com ISSN: 2319-8354

### **REFERENCES**

- 1.A. Zervos and C. Kjaer, *Pure Power: Wind Energy Scenarios for 2030*. Brussels, Belgium: European Wind Energy Association (EWEA),

- 2. on, "Grid code—High and extra high voltage," Bayreuth, Germany. Apr. 2006. [Online]. Available: http://www.pvupscale.org/IMG/pdf/ D4\_2\_DE\_annex\_A-3\_EON\_HV\_grid\_\_connection\_requirements\_ENENARHS2006de.pdf

- 3. PO-12.3 Requisitos de Respuesta Frente a Huecos de Tension de las Instalaciones Eolicas, Comisión Nacional de Energía, Madrid, Spain, Oct. 2006.

- 4. IEEE Standard for Interconnecting Distributed Resources With Electric Power Systems, IEEE Std. 1547-2003, 2003.

- 5. The Grid Code: Revision 31, National Grid Electricity Transmis-

- sion, Warwick, U.K., Oct. 2008, no. 3. [Online]. Available: http://www2. nationalgrid.com/uk/industry-information/electricity-codes/grid-code/

- 6. Elkraft System og Eltra, "Vindmuller tilsluttet net med sprindinger under 100 kv," Fredericia, Denmark, TF3.2.6, 2004. [Online]. Available: http://www.energinet.dk/SiteCollectionDocuments/Engelske%20dokumenter/El/Grid%20Code%203.2.5%20Wind%20Turbines%20connected%20above%20100%20kV.pdf

- 7. M. Tsili and S. Papathanassiou, "A review of grid code technical require-ments for wind farms," *IET Renew. Power Gen.*, vol. 3, no. 3, pp. 308–332, Sep. 2009.

- 8.F. Iov, A. Hansen, P. Sorensen, and N. Cutululis, "Mapping of Grid Faults and Grid Codes," Risø Nat. Lab., Roskilde, Denmark, Tech. Rep. Risoe-R-1617, 2007.

- 9.A. Luna, P. Rodriguez, R. Teodorescu, and F. Blaabjerg, "Low voltage ride through strategies for SCIG wind turbines in distributed power generation systems," in *Proc. IEEE PESC*, Jun. 15–19, 2008, no. 1, pp. 2333–2339.

- 10.D. Xiang, L. Ran, P. J. Tavner, and S. Yang, "Control of a doubly fed induction generator in a wind turbine during grid fault ride-through," *IEEE Trans. Energy Convers.*, vol. 21, no. 3, pp. 652–662, Sep. 2006.

- 11.J. Morren and S. W. H. de Haan, "Ridethrough of wind turbines with doubly-fed induction generator during a voltage dip," *IEEE Trans. Energy Convers.*, vol. 20, no. 2, pp. 435–441, Jun. 2005.

- 12.M. Molinas, J. A. Suul, and T. Undeland, "Low voltage ride through of wind farms with cage generators: STATCOM versus SVC," *IEEE Trans. Power Electron.*, vol. 23, no. 3, pp. 1104–1117, May 2008.

- 13.K. Li, J. Liu, Z. Wang, and B. Wei, "Strategies and operating point optimization of STATCOM control for voltage unbalance mitigation in three-phase three-wire systems," *IEEE Trans. Power Del.*, vol. 22, no. 1, pp. 413–422, Jan. 2007.

- 14.J. A. Barrena, L. Marroyo, M. A. R. Vidal, and J. R. T. Apraiz, "Indi-vidual voltage balancing strategy for PWM cascaded H-bridge converter-based STATCOM," *IEEE Trans. Ind. Electron.*, vol. 55, no. 1, pp. 21–29, Jan. 2008 Awad, J. Svensson, and M. Bollen, "Mitigation of unbalanced voltage dips using static series compensator," *IEEE Trans. Power Electron.*, vol. 19, no. 3, pp. 837–846, May 2004.

15. M. Bongiorno, J. Svensson, and A. Sannino, "An advanced cascade con-troller for series-connected VSC for voltage dip mitigation," *IEEE Trans. Ind. Appl.*, vol. 44, no. 1, pp. 187–195, Jan./Feb. 2008.

Mr JAGADEESH.PEDDAPUDI MTech(Ph.D) AssociateProfessor, Samskruti Engg college,Hyderabad, INDIA.

Mr BALACHANDRA REDDY.C MTech(Ph.D) AssociateProfessor, CBIT, Hyderabad,INDIA